RK3568核心板設備樹配置LVDS液晶屏驅動技術指南

摘要

本文詳細介紹了瑞芯微RK3568處理器在Linux環境下,如何通過設備樹(Device Tree)配置LVDS(Low-Voltage Differential Signaling)液晶屏驅動。我們將深入探討LVDS接口的原理、設備樹中的關鍵節點、時序參數配置以及常見問題排查,旨在為硬件和軟件工程師提供一套完整且實用的配置指南,確保LVDS液晶屏在RK3568平臺上穩定、高效地工作。

1. RK3568與LVDS液晶屏概述

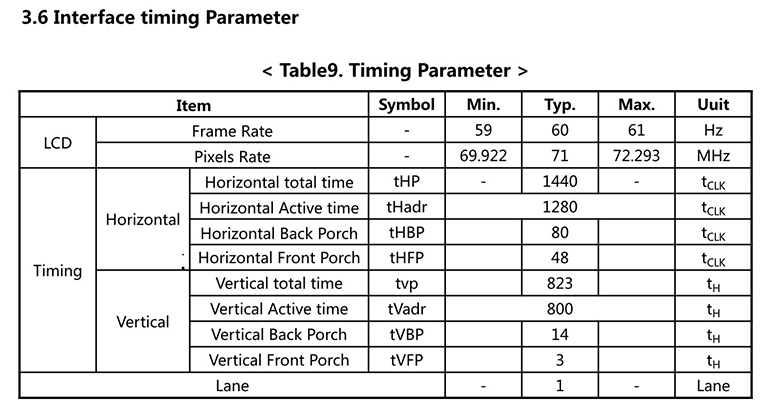

瑞芯微RK3568是一款高性能、低功耗的通用型SoC,廣泛應用于智能NVR、云終端、IoT網關、工控平板等領域。它集成了強大的多媒體處理能力,支持多種顯示接口,其中LVDS是工業和車載領域常用的顯示接口,以其抗干擾能力強、傳輸距離遠、功耗低等優點而備受青睞。LVDS液晶屏通過差分信號傳輸圖像數據,需要精確的時序和正確的配置才能正常顯示。在Linux系統中,設備樹(Device Tree)是描述硬件信息的核心機制,對于RK3568這類復雜的SoC,所有外設(包括顯示控制器和LVDS接口)的配置都通過設備樹來完成,下面基于WTC-RK3568核心板的硬件,采用BOE的一款液晶屏來做為例子來配置下,型號是EV101WXM,參數如下:

圖一 液晶屏時序參數

2. 設備樹配置基礎

設備樹是Linux內核用于描述硬件拓撲結構的數據結構。對于RK3568,其設備樹文件通常位于內核源碼的 arch/arm64/boot/dts/rockchip/ 目錄下,例如 rk3568-evb.dts 或 rk3568-xxx-board.dts。配置LVDS液晶屏驅動,主要涉及以下幾個方面:

●LVDS控制器配置:RK3568內部的LVDS控制器負責生成LVDS信號。

● LVDS PHY配置:LVDS物理層(PHY)負責將數字信號轉換為LVDS差分信號。

● 面板(Panel)信息:描述所連接LVDS液晶屏的具體參數,包括分辨率、時序、背光控制等。

● 顯示路由配置:確保顯示數據正確地從RK3568內部顯示控制器路由到LVDS輸出。

3. LVDS設備樹關鍵節點與屬性配置

在RK3568的設備樹中,LVDS液晶屏的配置通常涉及 &lvds 節點和 lvds-panel 子節點。

3.1 LVDS控制器節點 (&lvds)

這個節點主要配置LVDS控制器的工作模式和與面板的連接關系。

&lvds {

status = "okay"; // 使能LVDS控制器

ports {

#address-cells =<1>;

#size-cells =<0>;

port@1 {

reg =<1>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>; // 指向面板的輸入端點

};

};

};

};

關鍵屬性解釋:

* status = "okay": 啟用LVDS控制器。

* ports: 定義控制器與面板之間的連接關系。lvds_out_panel 是LVDS控制器的輸出端點,它通過 remote-endpoint 指向面板的輸入端點 panel_in_lvds。

3.2 LVDS PHY節點 (&lvds_phy)

LVDS PHY通常是RK3568內部的一個獨立模塊,負責LVDS信號的物理層特性。

&lvds_phy {

status = "okay"; // 使能LVDS PHY

rockchip,grf = <&grf>; // 引用GRF寄存器

rockchip,phy-supply = <&vcc_3v3>; // LVDS PHY的供電,根據實際原理圖配置

};

關鍵屬性解釋:

* status = "okay": 啟用LVDS PHY。

* rockchip,phy-supply: 指定LVDS PHY的供電電源。這需要根據你的硬件原理圖來確定,確保電源節點正確引用。

3.3 面板(Panel)節點 (lvds-panel)

這是配置LVDS液晶屏核心參數的地方,包括分辨率、時序、背光、電源時序等。

lvds-panel {

compatible = "simple-panel"; // 通用面板兼容性

power-supply = <&vcc_3v3>; // 面板供電電源,根據實際原理圖配置

backlight = <&backlight>; // 引用背光控制器節點

enable-gpios = <&gpio0 rk_pc5="" gpio_active_high="">; // 面板使能GPIO,根據實際原理圖配置

// 面板電源/使能時序控制

prepare-delay-ms =<20>; // 面板準備(如供電)后的延時

enable-delay-ms =<20>; // 面板使能信號后的延時

disable-delay-ms =<20>; // 面板禁用信號后的延時

unprepare-delay-ms =<20>; // 面板去準備(如斷電)前的延時

// LVDS總線數據格式

bus-format =; // 媒體總線格式,這里是RGB888,單通道7對差分線,4對控制線,SPWG標準

// 面板物理尺寸

width-mm =<217>; // 面板寬度(毫米)

height-mm =<136>; // 面板高度(毫米)

// 屏幕分辨率和時序參數 (重要!)

display-timings {

native-mode = <&timing0>; // 指定原生模式為timing0

timing0: timing0 {

// 像素時鐘頻率 (單位: Hz)

clock-frequency =<71000000>; // 例如,71MHz

// 水平時序

hactive =<1280>; // 水平有效像素

hback-porch =<80>; // 水平后沿

hfront-porch =<48>; // 水平前沿

hsync-len =<32>; // 水平同步脈沖寬度

hsync-active =<0>; // 水平同步信號極性 (0: 低有效, 1: 高有效)

// 垂直時序

vactive =<800>; // 垂直有效像素

vback-porch =<14>; // 垂直后沿

vfront-porch =<3>; // 垂直前沿

vsync-len =<6>; // 垂直同步脈沖寬度

vsync-active =<0>; // 垂直同步信號極性 (0: 低有效, 1: 高有效)

// 數據使能和像素時鐘極性

de-active =<0>; // 數據使能信號極性 (0: 低有效, 1: 高有效)

pixelclk-active =<0>; // 像素時鐘極性 (0: 下降沿, 1: 上升沿)

};

};

port {

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>; // 指向LVDS控制器的輸出端點

};

};

};

新增屬性解釋:

●prepare-delay-ms, enable-delay-ms, disable-delay-ms, unprepare-delay-ms: 這些是面板電源和使能時序的延時參數,用于確保面板在正確的時間上電、使能、禁用和斷電,避免時序沖突導致顯示異常。具體數值應參考液晶屏數據手冊。

●bus-format =;: 這定義了LVDS總線上傳輸數據的格式。

●RGB888: 表示每個像素使用RGB 8位數據。

●1X7X4: 通常指單通道(1X),7對數據差分線(7X),4對控制差分線(4X)。這是一種非標準但常見的LVDS配置表示方式,具體含義需結合芯片手冊和面板手冊確認。

●SPWG: 可能指的是某種特定的LVDS標準或模式,如SPWG-LVDS。

● width-mm, height-mm: 面板的物理尺寸,用于系統計算DPI(每英寸點數)。

● de-active: 數據使能信號(Data Enable)的極性。

3.4 顯示路由節點 (&lvds_in_vp1, &route_lvds)

這些節點負責RK3568內部顯示數據路徑的路由,確保圖像數據從視頻處理器正確地發送到LVDS控制器。

&lvds_in_vp1 {

status = "okay"; // 使能LVDS輸入到視頻處理器1的路由

};

&route_lvds {

status = "okay"; // 使能LVDS路由

charge_logo,mode = "center"; // 充電Logo顯示模式,例如居中

connect = <&vp1_out_lvds>; // 連接到視頻處理器1的LVDS輸出

};

關鍵屬性解釋:

●&lvds_in_vp1: 表示LVDS信號輸入到視頻處理器1的路徑。

●&route_lvds: 定義LVDS顯示數據的具體路由方式,包括充電Logo的顯示模式以及連接到哪個視頻輸出端口。

3.5 其他顯示控制器狀態 (&dsi0, &dsi1, &video_phy0, &video_phy1)

根據您的配置,其他MIPI DSI控制器被禁用,而特定的視頻PHY被使能。

&dsi0 {

status = "disabled"; // 禁用DSI0控制器

};

&dsi1 {

status = "disabled"; // 禁用DSI1控制器

};

&video_phy0 {

status = "okay"; // 使能視頻PHY0

};

&video_phy1 {

status = "disabled"; // 禁用視頻PHY1

};

關鍵屬性解釋:

● &dsi0, &dsi1: 明確禁用MIPI DSI控制器,這表明LVDS輸出不是通過DSI控制器切換模式實現,而是通過獨立的LVDS控制器 (&lvds)。

● &video_phy0, &video_phy1: 控制視頻物理層接口的狀態。video_phy0 的使能通常與LVDS輸出路徑相關。

4. 背光(Backlight)配置

LVDS液晶屏通常需要獨立的背光控制。RK3568可以通過PWM或GPIO來控制背光亮度。

4.1 PWM背光控制

&pwm5 { // 使用PWM5控制器

status = "okay";

};

backlight: backlight {

compatible = "pwm-backlight";

pwms = <&pwm5 0="" 25000="">; // PWM5通道0, 周期25000ns (40KHz), 極性0 (正常)

brightness-levels = <

0 20 20 21 21 22 22 23 23 24 24 25 25 26 26 27

27 28 28 29 29 30 30 31 31 32 32 33 33 34 34 35

35 36 36 37 37 38 38 39 40 41 42 43 44 45 46 47

48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79

80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95

96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111

112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127

128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143

144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159

160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175

176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191

192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207

208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223

224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239

240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255

>; // 亮度等級

default-brightness-level =<200>; // 默認亮度

post-pwm-on-delay-ms =<10>; // PWM開啟后的延時

pwm-off-delay-ms =<10>; // PWM關閉前的延時

status = "okay";

};

新增屬性解釋:

● post-pwm-on-delay-ms: PWM開啟后的延時,用于確保背光控制器穩定后再進行其他操作。

● pwm-off-delay-ms: PWM關閉前的延時,用于確保背光平穩關閉。

4.2 GPIO背光控制

如果背光只是簡單的開關控制,可以使用GPIO。

backlight: backlight {

compatible = "gpio-backlight";

gpios = <&gpio0 rk_pb1="" gpio_active_high="">; // 背光控制GPIO

default-on; // 默認開啟背光

status = "okay";

};

5. 完整設備樹示例 (基于您提供的配置)

以下是根據您提供的配置片段整理的RK3568設備樹示例。請注意,這仍然是一個片段,需要集成到您的主設備樹文件(如 rk3568-xxx-board.dts)中。

// 在你的rk3568-xxx-board.dts或rk3568.dtsi中添加或修改

#include// 包含GPIO定義

#include// 包含媒體總線格式定義

&grf {

// 可能需要配置一些LVDS相關的GRF寄存器

// 例如,LVDS PHY的IO復用等

};

&lvds {

status = "okay";

ports {

#address-cells =<1>;

#size-cells =<0>;

port@1 {

reg =<1>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>;

};

};

};

};

&lvds_phy {

status = "okay";

rockchip,grf = <&grf>;

rockchip,phy-supply = <&vcc_3v3>; // 假設LVDS PHY由3.3V供電

};

// 假設vcc_3v3是你的3.3V電源節點,如果不是,請根據實際原理圖修改

&vcc_3v3 {

regulator-name = "vcc_3v3";

regulator-always-on;

regulator-boot-on;

status = "okay";

};

&pwm5 { // 使用PWM5控制器控制背光

status = "okay";

};

lvds-panel {

compatible = "simple-panel";

power-supply = <&vcc_3v3>; // 面板供電電源

backlight = <&backlight>;

enable-gpios = <&gpio0 rk_pc5="" gpio_active_high="">; // 面板使能GPIO為GPIO0_PC5

prepare-delay-ms =<20>;

enable-delay-ms =<20>;

disable-delay-ms =<20>;

unprepare-delay-ms =<20>;

bus-format =;

width-mm =<217>;

height-mm =<136>;

// BOE,EV101WXM-N10

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency =<71000000>;

hactive =<1280>;

vactive =<800>;

hback-porch =<80>;

hfront-porch =<48>;

vback-porch =<14>;

vfront-porch =<3>;

hsync-len =<32>;

vsync-len =<6>;

hsync-active =<0>; // 低有效

vsync-active =<0>; // 低有效

de-active =<0>; // 低有效

pixelclk-active =<0>; // 下降沿有效

};

};

port {

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>;

};

};

};

backlight: backlight {

compatible = "pwm-backlight";

pwms = <&pwm5 0="" 25000="">; // PWM5通道0, 周期25000ns (40KHz), 極性0 (正常)

brightness-levels = <

0 20 20 21 21 22 22 23 23 24 24 25 25 26 26 27

27 28 28 29 29 30 30 31 31 32 32 33 33 34 34 35

35 36 36 37 37 38 38 39 40 41 42 43 44 45 46 47

48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79

80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95

96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111

112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127

128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143

144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159

160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175

176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191

192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207

208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223

224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239

240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255

>;

default-brightness-level =<200>;

post-pwm-on-delay-ms =<10>;

pwm-off-delay-ms =<10>;

status = "okay";

};

&lvds_in_vp1 {

status = "okay";

};

&route_lvds {

status = "okay";

charge_logo,mode = "center";

connect = <&vp1_out_lvds>;

};

&dsi0 {

status = "disabled";

};

&dsi1 {

status = "disabled";

};

&video_phy0 {

status = "okay";

};

&video_phy1 {

status = "disabled";

};

6. 編譯與燒錄設備樹

完成設備樹修改后,需要重新編譯設備樹并燒錄到RK3568設備中。

7. 總結

通過本文的詳細介紹,相信您對RK3568設備樹配置LVDS液晶屏驅動有了更深入的理解。核心在于精確匹配液晶屏數據手冊中的時序參數,并正確配置RK3568內部的LVDS控制器和PHY以及顯示路由。在實際開發中,采用Weathink RK3568核心板可以極大地簡化硬件復雜度,讓您更專注于軟件配置和調試。耐心細致的排查和對硬件的深刻理解是成功的關鍵。希望這份指南能幫助您順利點亮LVDS液晶屏,加速您的RK3568項目開發進程。

如果您在項目開發過程中,對RK3568硬件設計、LVDS液晶屏驅動或Weathink核心板有任何疑問,需要更深入的技術支持或定制化服務,歡迎隨時聯系我們:

聯系人: 林偉

郵箱: lw@weathink.com

電話: 18072728558

EN

EN