瑞芯微RK3568 USB3.0 HOSTA 原理圖與走線Layout設計指南

瑞芯微RK3568 USB3.0 HOSTA 原理圖與走線Layout設計指南

1. 概述

瑞芯微RK3568是一款高性能、低功耗的處理器,廣泛應用于智能終端、邊緣計算等領域。其內置的USB3.0控制器支持USB3.0 HOSTA接口,可提供高達5Gbps的數據傳輸速率。本文將詳細介紹基于維芯科WTC-RK3568S核心板,就RK3568 USB3.0 HOSTA接口的原理圖設計和走線Layout要點,幫助開發者實現穩定可靠的USB3.0連接。

圖一 USB3.0 HOSTA

2. 原理圖設計

1.1 電源設計

VBUS供電: USB3.0 HOSTA接口需要為連接的設備提供VBUS電源,典型電壓為5V。建議使用獨立的DC-DC電源芯片為VBUS供電,并預留足夠的電流余量(至少1A)。

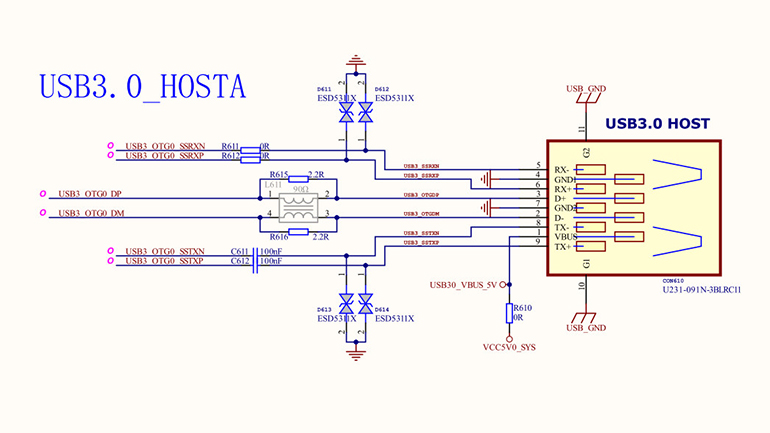

1.2 信號連接

差分信號對: USB3.0 HOSTA接口包含兩對差分信號:TX+/TX- 和 RX+/RX-。需要將RK3568的USB3.0 HOSTA接口的差分信號引腳與USB連接器的對應引腳正確連接。

單端信號: USB3.0 HOSTA接口還包含一些單端信號,例如VBUS、D+、D-、ID、GND等。需要將這些信號與USB連接器的對應引腳正確連接。

1.3 ESD防護

為了增強USB3.0 HOSTA接口的ESD防護能力,建議在差分信號線上添加ESD防護器件,例如TVS二極管。另外D+、D-信號線上增加2.2R的電阻能夠一定程度上保護芯片。USB3座子所有信號都必須增加TVS管,TVS器件盡可能靠近USB連接器放置。對于SSTXP/N,SSRXP/N信號,TVS的最大結電容不應超過0.4pF。

圖二 RK3568 USB3.0連接圖

3. 走線Layout設計

3.1 差分信號走線

●阻抗控制: USB3.0差分信號的特性阻抗為90Ω。需要使用阻抗計算工具計算PCB走線的寬度和間距,并使用阻抗測試儀器進行驗證。

● 等長走線: SSTXP/N,SSRXP/N差分對應嚴格遵循差分規則走線。例如,必須保持相同的長度、相同的寬度、相同的層和固定的線距,并盡可能保持對稱,對內線長延遲控制在12mil以內。

● 減少過孔: 盡量減少差分信號線上的過孔數量,過孔會引入阻抗不連續和信號反射。SSTXP/N和SSRXP/N盡量走在TOP層,必須要換層時,不得超過2個過孔,并靠近信號過孔放置對稱的縫合地孔,縫合地孔和信號過孔中心距不得超過30mil,走線拐角盡量用弧線或者鈍角,不能為直角或銳角。

避免交叉: 避免差分信號線與其他信號線交叉,特別是高速信號線。

3.2 電源走線

加粗走線: VBUS和VDDIO電源走線需要加粗,以減小阻抗和壓降。

添加濾波電容: 在VBUS和VDDIO電源引腳附近添加適量的濾波電容,以濾除電源噪聲。

3.3 地平面

●完整地平面: 保持完整的地平面,為信號提供良好的回流路徑。SSTXP/N,SSRXP/N信號的參考層需要為完整的地平面,避免出現連續的過孔阻斷信號的回流路徑的情況

●分割地平面: 如果需要分割地平面,需要使用磁珠或0歐姆電阻將不同地平面連接起來。

4. 其他注意事項

●仿真驗證: 可以使用信號完整性仿真工具對USB3.0 HOSTA接口的信號完整性進行仿真驗證,確保信號質量滿足要求。

●測試驗證: 在PCB板制作完成后,需要使用示波器等儀器對USB3.0 HOSTA接口的信號進行測試驗證,確保信號質量符合規范。

●共模電感:在USB差分信號上預留共模電感,提供改善EMI一個手段

5. 總結

RK3568 USB3.0 HOSTA接口的原理圖和走線Layout設計需要遵循一定的規范,以確保信號完整性和系統穩定性。本文介紹了RK3568 USB3.0 HOSTA接口的原理圖設計、走線Layout設計以及其他注意事項,希望能夠幫助開發者更好地完成相關設計工作。

杭州維芯科電子有限公司作為專業的主板設計公司,在USB3.0的使用上較為成熟,歡迎隨時聯系維芯科,我司提供的自主設計RK3568核心板,穩定可靠的工控機。

http://www.bestoptometry.cn/products/hexinban/12.html

EN

EN